A few years back I wrote a RISC-V core and a DVI output demo and back then I mentioned I would add extra features to both of them. The past few years I not only updated my RISC-V core, but also combined it with the DVI output core to create basically a SOC.

The RISC-V core now can run GCC compiled code, so no need for hand written assembly code anymore. There are still several key features missing, like IRQ/Trap support (which makes it impossible to run some sort of OS at the moment).

The DVI output core was rewritten to be a true HDMI output core. The reason to do this was so it would be possible to also output audio. The output resolution is still 1920x1080 with an update rate of 30Hz, the reason that 1920x1080@30 is used and not 1920x1080@60 is because the needed 742.25MHz TMDS speed is beyond the 400MHz limit of the used FPGA. So or the resolution needs to be reduced, or the refresh rate needs to be reduced. Reducing the resolution would mean using a resolution that is not native to most monitors, so I reduced the refresh rate from 60Hz to 30Hz so the TMDS signal speed was reduced to 371.25MHz.

The HDMI output would be rather useless if there is nothing that generates something to display. On a modern computer that would be the task of the GPU, on a C64 it was the task of the VIC, and on the Amiga it was the task of Agnus and Denise. On my SOC it is the task of the Video Processing Unit, or VPU for short.

VPU

The VPU currently has the following features

- resolution of 640x360 with indexed 256 colors per pixel.

- 1 bitmap plane, which is read from main memory by DMA.

- 1 tile plane, which is read from main memory by DMA.

- 8x8 tile map that can have 256 indexed colors per pixel.

- 80x45 tile resolution.

- 32 sprites with indexed 256 colors per pixel.

- max size 4096 bytes, (1x4096, 2x2048, 4x1024, … 64x64 .. 2048x2, 4096x1)

- programmable border

- order of bitmap, tile, sprites, and border can be programmed.

- color index 0 is always transparent.

- programmable background color, in case a “transparent” pixel has to be displayed.

There are still a lot of features missing, like the possibility to generate VSYNC-IRQs (partly because the RISC-V core does not yet do IRQ handling).

SPU

Like a C64, Amiga, or PC, video is one thing, but audio is also a key feature. The C53 is famous for its SID chip, the Paula in the Amiga for its sample output. On my SOC it is the task of the Sound Processing Unit, or SPU for short.

The SPU currently has the following features

- 16 bit 48ksample/second stereo output (via HDMI)

- 8 voices

- generator for pulse, saw, triangle, noise

- ADSR envelop generator

- programmable LP, HP, BP, BR filters

- each voice can be output to the left and right

- master volume control for left and right

Here there are also still feature missing, like the possibility to use samples, and sine wave generation.

Boot Monitor

To speed up program development the SOC has a small boot monitor in the FPGA image that supports uploading a program via XMODEM. This program can than be started by a command send via the same UART.

Demo time

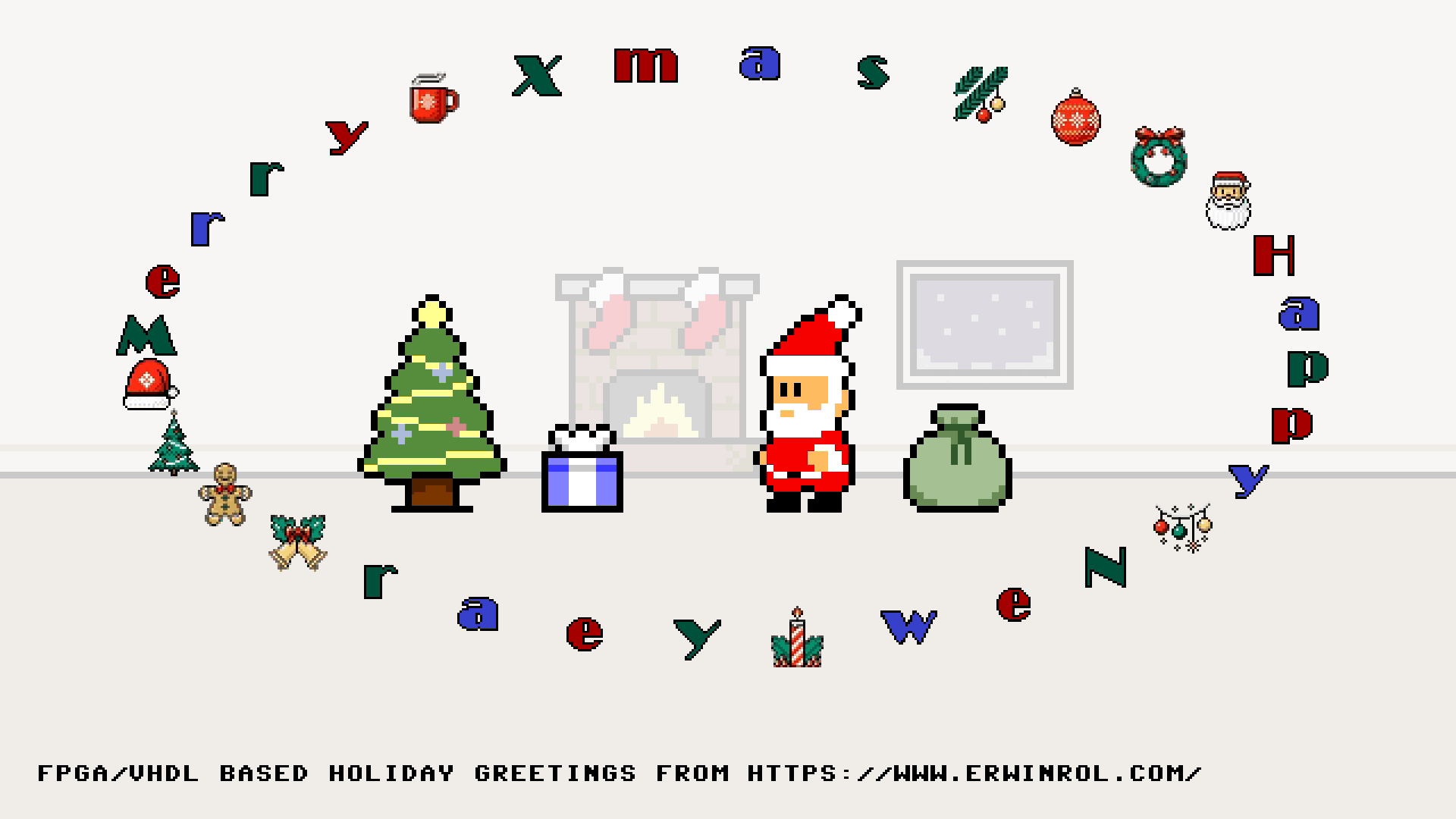

After putting everything together I created the X-mas Demo, that you probably already watched. Eventhough it might look like a C64, it isn’t, the start up screen is just the tile mode plane using a C64 tile map. The main screen graphics are just all 32 sprites rotating over a bitmap background. The audio on the other hand is an actual C64 SID file running on an C64 emulator, because SID files are actual C64 programs not simple data files. The original SID file can be found here.

To be honest I am surprised it all works that well.

And for now Merry X-mas and a Happy New Year to everybody!

Feedback

Feel free to give feedback on Linkedin or YouTube