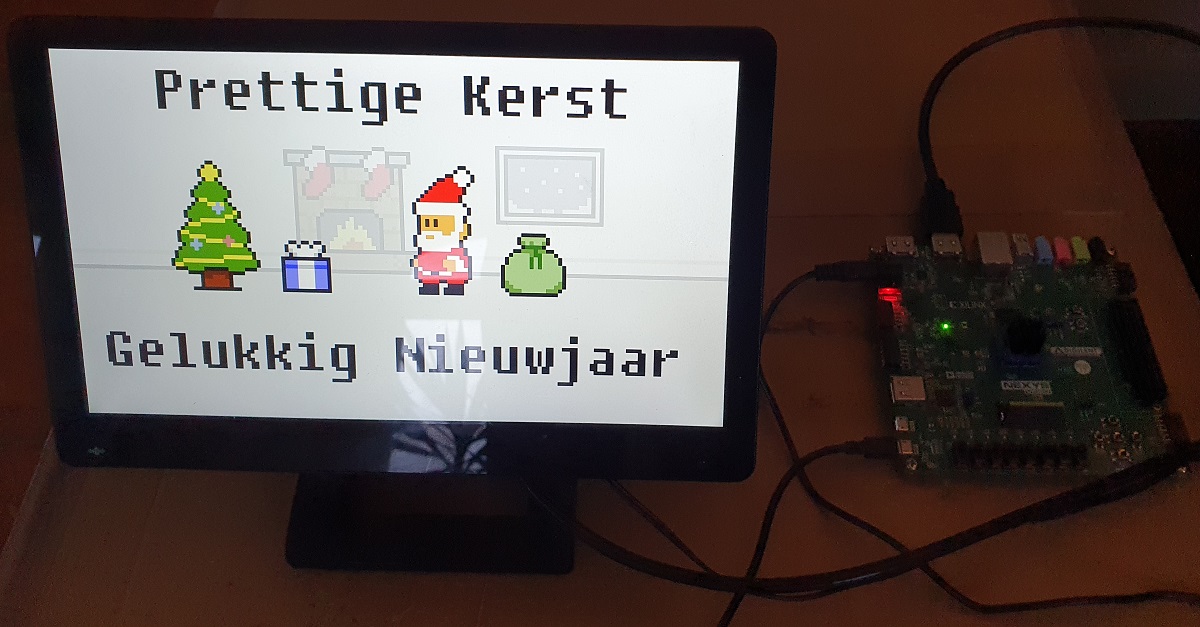

Prettige Kerst

Merry X-Mas

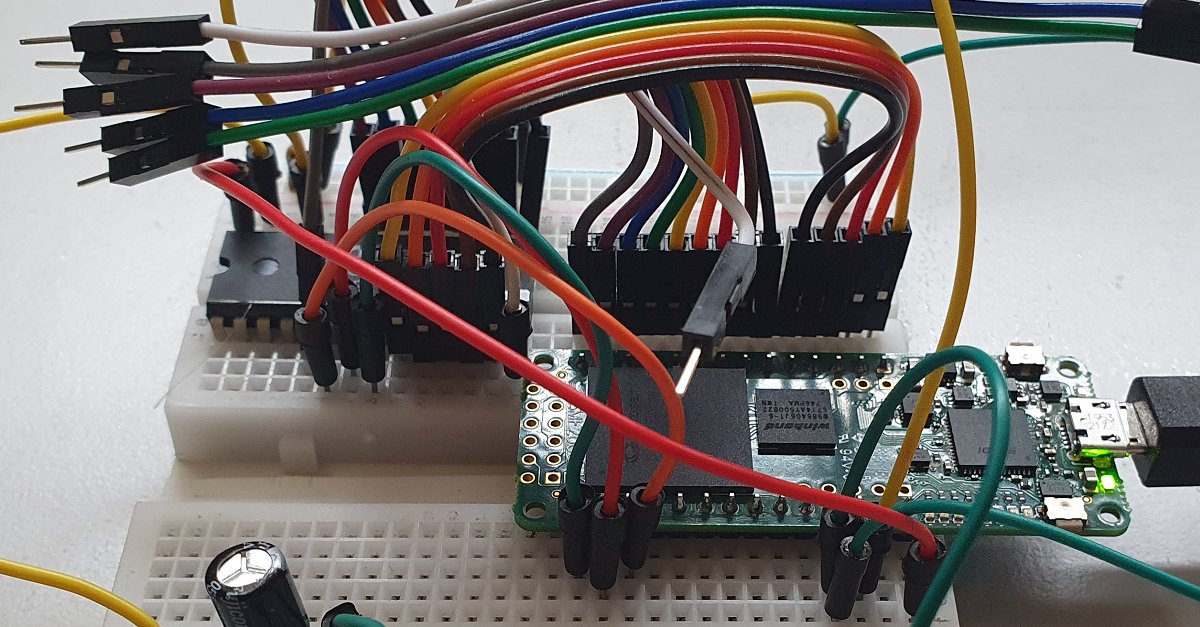

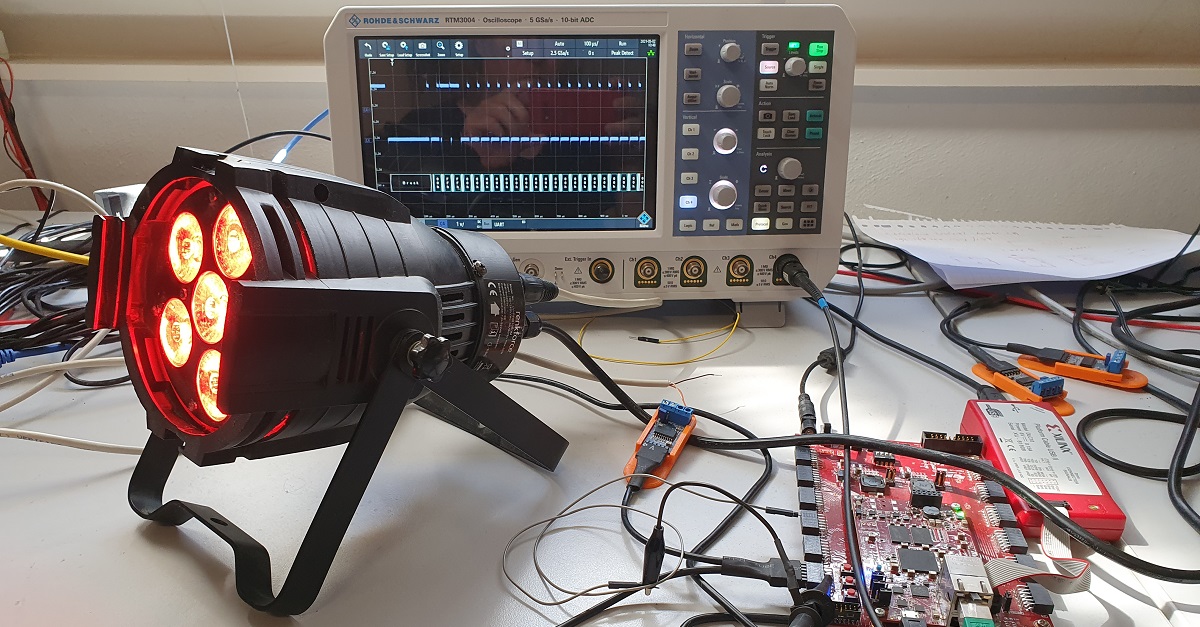

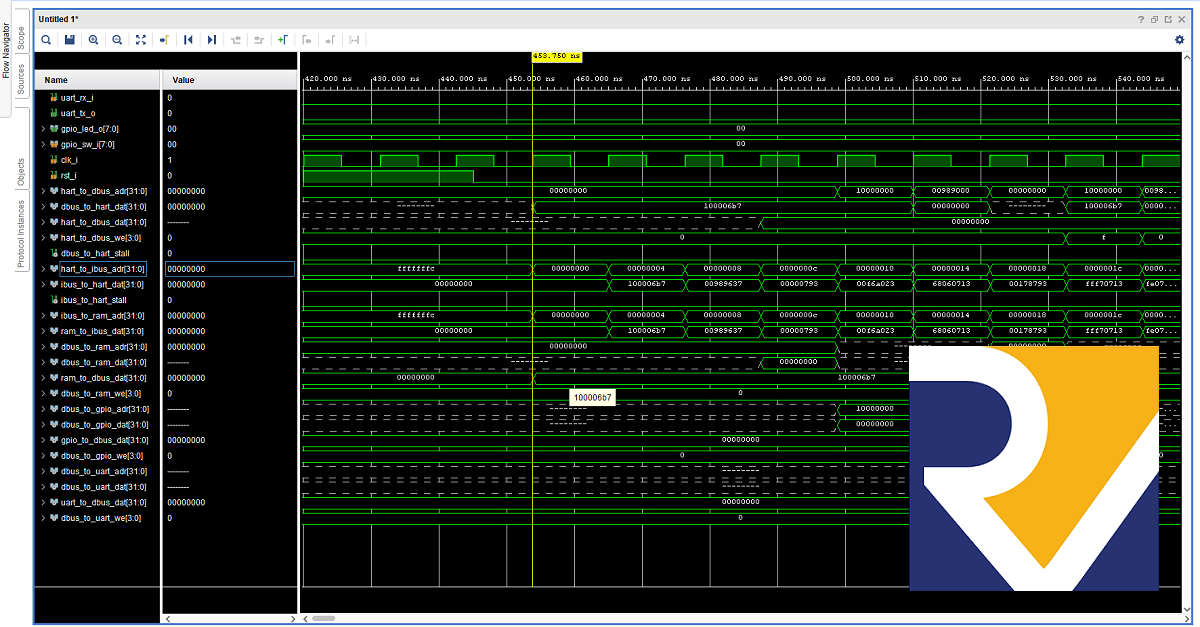

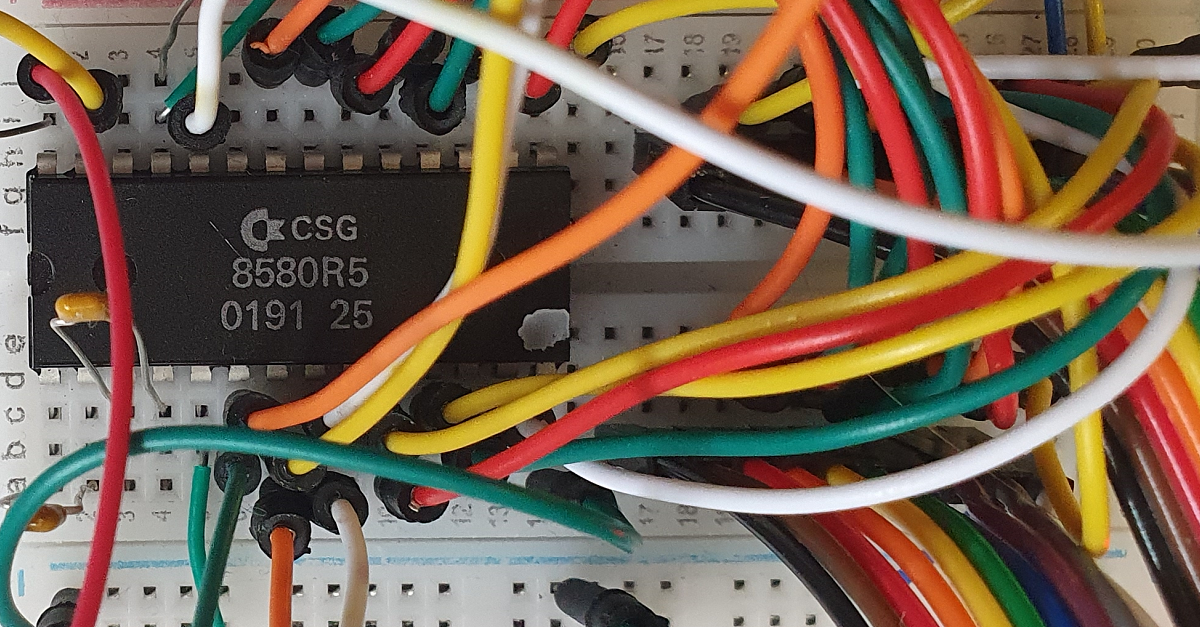

A few years back I wrote a RISC-V core and a DVI output demo and back then I mentioned I would add extra features to both of them. The past few years I not only updated my RISC-V core, but also combined it with the DVI output core to create basically a SOC.

The RISC-V core now can run GCC compiled code, so no need for hand written assembly code anymore.

[Read More]